Elective Course & Field Recommendation System

5 Member Group

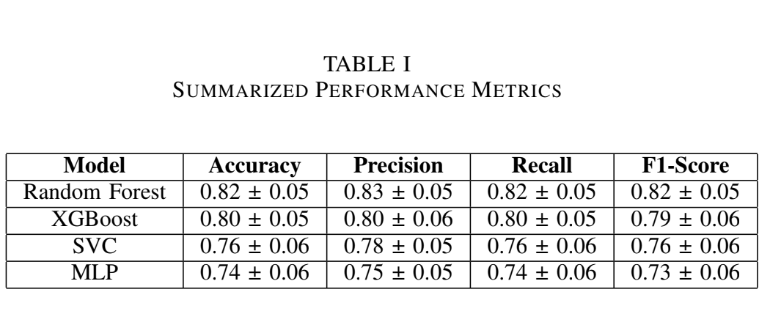

Developed an intelligent Elective Course Recommendation System using machine learning

models including SVM, LDA, and Multilayer Perceptron (MLP).

Designed and implemented the overall system architecture, and established a complete

MLOps pipeline using ZenML for reproducible experimentation and

streamlined model lifecycle management.

Deployed the solution on Google Cloud Platform, integrating model

serving, storage, and performance monitoring.

Actively contributed to data preprocessing, training pipeline, evaluation metrics, and

scalable deployment strategies.

Mar 2024 – Aug 2024

💻 View on GitHub